CPU-Entlastung

Vorverarbeitung auf Framegrabbern mit FPGA-Design-Kit

Kamerahersteller und Integratoren haben ab sofort die Möglichkeit selbstständig Code in das FPGA der Framegrabber Coaxlink Octo und Coaxlink Quad CXP12 hochzuladen. So ist die Ausführung von Aufgaben möglich, die bisher auf dem Host verarbeitet wurden.

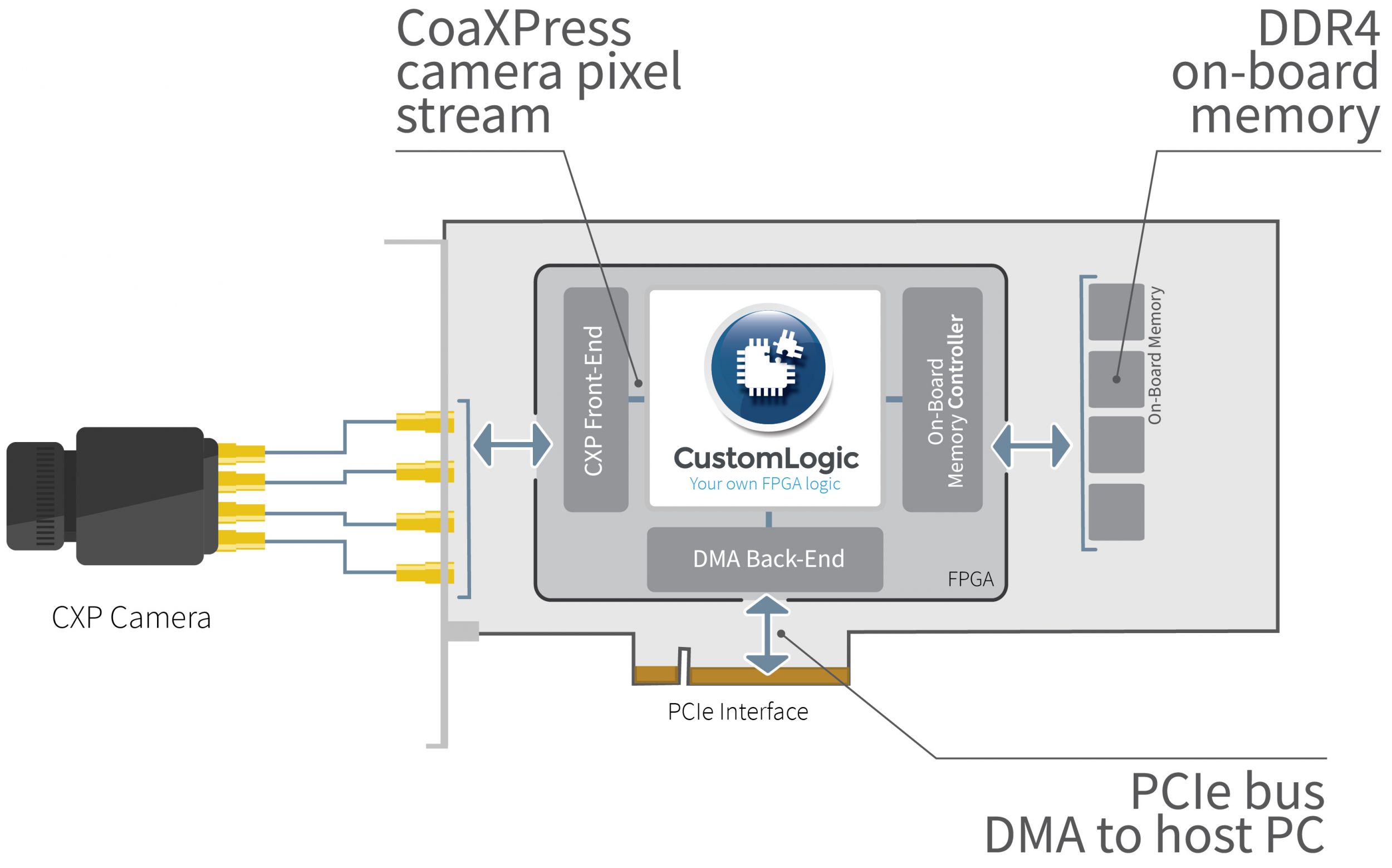

Mit dem FPGA-Design-Kit CustomLogic können Anwender ihren eigenen FPGA-Code in einer Objektdatei erstellen, kompilieren und anschließend in das FPGA der Framegrabber hochladen. (Bild: Euresys s.a.)

Mit dem CustomLogic FPGA-Design-Kit können praktisch alle sich wiederholenden Bildverarbeitungsaufgaben umgesetzt werden, die für jedes Pixel im Bild ausgeführt werden. Typische Anwendungen sind die Umwandlung des Bildes anhand einer Lookup-Tabelle, wie z.B. die Farbkonvertierung von der RGB- zur YUV-Skala, die Implementierung eines Rauschreduzierungsalgorithmus oder die Korrektur von Sensordefekten, wie schwarzen Pixeln. Eine weitere Anwendung ist die Flat-Field-Korrektur, wobei Lichtintensitätsunterschiede im gesamten Sichtfeld korrigiert werden. Das FPGA verarbeitet dabei das Bild parallel mit der Bildübertragung. So wird ohne Verzögerungen dank des Framegrabbers Verarbeitungszeit auf dem Hostcomputer eingespart. Dadurch bieten Vision-Systeme eine höhere Auflösung und Geschwindigkeit sowie geringere Latenzen ohne höhere Kosten für den Hostcomputer.

FPGA-Code selbst hochladen

Früher boten Hersteller von Framegrabbern den Kunden an, deren applikationsspezifischen Code in die FPGAs der Framegrabber einzubinden. Bei diesem Ansatz müssen die Anwender jedoch ihre entsprechenden Codes und Algorithmen dem Hersteller preisgeben. Bei CustomLogic von Euresys ist das nicht der Fall. Hier können die Anwender ihren eigenen FPGA-Code in einer Objektdatei erstellen, kompilieren und anschließend in das FPGA hochladen. Der proprietäre Code des Vision-Integrators verlässt dabei niemals den Standort. Viele große Maschinenbauer haben in der Vergangenheit ihre eigenen Framegrabber auf Basis von FPGAs entwickelt, die auch Bildverarbeitungs- und Analyseaufgaben ausführen. Diese Framegrabber nutzen meist das alte CameraLink-Protokoll. Diese Anwender stehen aber derzeit vor der Herausforderung, ihre Framegrabber an die aktuelle Generation der High-Speed-Schnittstellen wie beispielsweise CXP-12 anzupassen. Diese Aufgabe wird nun wesentlich vereinfacht, indem sie das CustumLogic Tool nutzen, um ihre proprietären Bildverarbeitungsroutinen auf die Framegrabbern hochzuladen.