Deep Learning für jedermann

Implementierung neuronaler Netze auf FPGAs – Teil 2/2

Welche Rolle spielen FPGAs bei Deep Learning? Im ersten Teil ging es um die Vorzüge der Technologie und das Ausführen trainierter CNN im Vergleich zu GPUs/CPUs. Dieses Mal geht es nun um die Implementierung auf FPGAs.

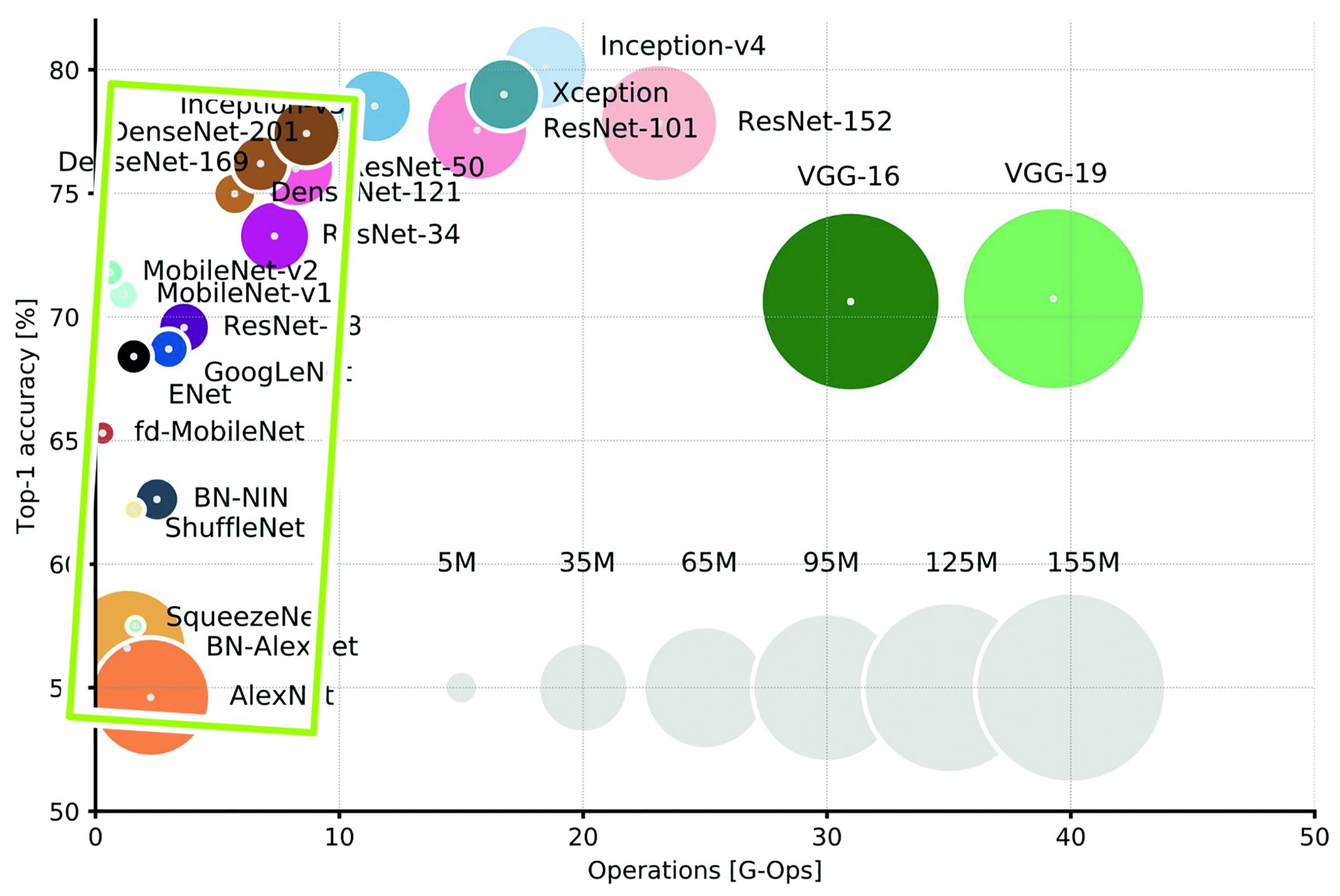

An analysis of Deep Neural Network Models for Pratical Applications (Alfredo Canziani, Adam Paszke, Eugenio Culurciello, 2017). (Bild: Silicon Software GmbH)

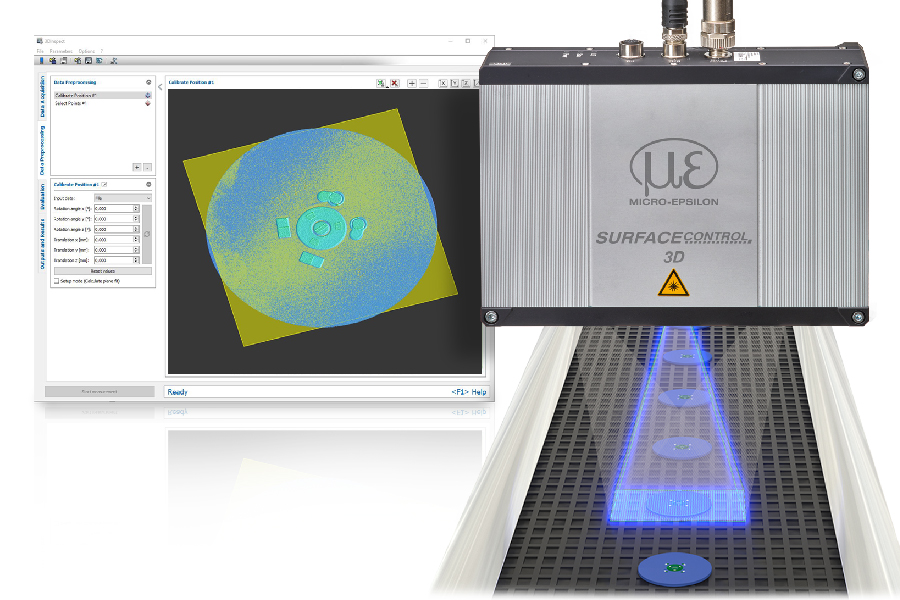

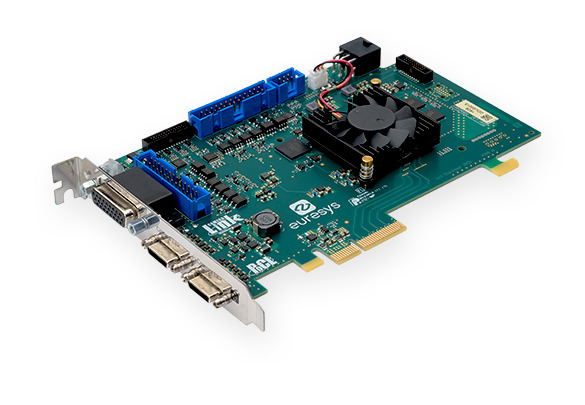

Die Rechenleistung von FPGAs hat sich in einem Maße entwickelt, die das Wachstum von herkömmlichen Prozessoren deutlich überflügelt. Der Produktionsprozess von FPGAs wird aktuell von 16 auf 7nm umgestellt, das heißt eine Vervielfachung der Logikreserven um den Faktor 10. Mit der Umstellung auf 3nm in ca. fünf Jahren wird sogar ein Faktor 100 im Vergleich zu heute erreicht. Dadurch lassen sich komplexe Algorithmen implementieren und Objekte in einem Bild automatisch klassifizieren. Um die bei vielen Deep Learning Anwendungen geforderte hohe Rechengeschwindigkeit zusammen mit einer hohen Durchsatzrate und Treffgenauigkeit zu erzielen sowie für die Implementierung großer Netze sind allerdings auch leistungsfähigere FPGAs notwendig. Für die in der Produktion erforderlichen Verarbeitungsgeschwindigkeiten stehen bereits Hochleistungs-Framegrabber und eingebettete Bildverarbeitungsgeräte wie Kameras und Sensoren mit größeren FPGAs zur Verfügung. Mit umfangreicheren FPGA-Ressourcen lassen sich komplexere Architekturen und damit auch Anwendungen verarbeiten. Die höhere Datenbandbreite ermöglicht eine Verarbeitung eines Gesamtbildes oder zusätzliche Bildvor- und -nachverarbeitung auf dem FPGA. Sie ist ausreichend hoch, um z.B. den kompletten Datenausgang einer GigE Vision Kamera mit Deep Learning zu analysieren.

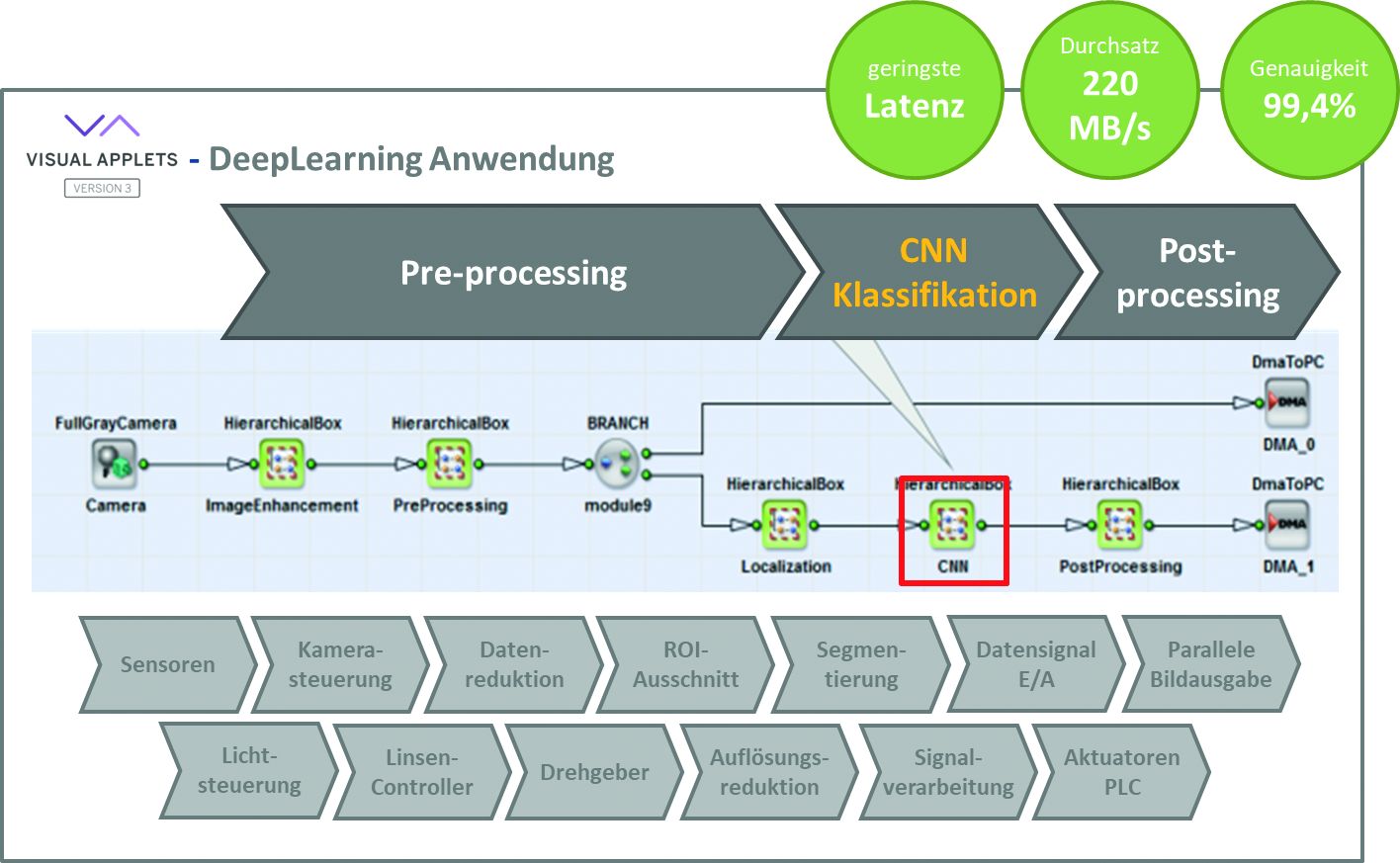

Verarbeitung von Gesamtern, Videos und Signalen in Echtzeit mit FPGAs unter Visual Applets. (Bild: Silicon Software GmbH)

FPGA-Ressourcen optimieren

Die Bearbeitungsmöglichkeiten im FPGA stehen im direkten Zusammenhang mit den verfügbaren Logikressourcen. Diese können für die algorithmische Beschreibung, aber auch für aufwändige Implementierungsmethoden, Rechentiefen oder höhere Bandbreiten über die Vervielfachung des Rechenkerns eingesetzt werden. Für Deep Learning gibt es unterschiedliche Methoden, Ressourcen einzusparen ohne die Qualität der Klassifizierung zu beeinträchtigen. Eine Methode ist die Skalierung der Bilder, die den internen Datendurchfluss reduziert. Erfahrungswerte haben gezeigt, dass die Rechentiefe sich nur marginal auf die spätere Erkennungsgenauigkeit durchschlägt. Die Reduktion von 32Bit auf 8Bit und von Floating Point auf Fixed Point / Integer ermöglicht dem FPGA, seine stark eingesparten Ressourcen in größere Netzarchitekturen zu investieren. Die höhere Rechengenauigkeit einer 32Bit Floating Point GPU ist für die Deep Learning Inference von geringer Bedeutung, erreichen doch 8Bit Fixed Point FPGAs eine ausreichend präzise Erkennungsgenauigkeit für die meisten Deep Learning Anwendungen bei zu vernachlässigender Fehlertoleranz. Bei Anforderungen nach besonders präziser Rechengenauigkeit lässt sich auf einem größeren FPGA als Ressourcenkompromiss auch 16Bit Fixed Point implementieren. Typische Aufgabenstellung in der Bildverarbeitung ist die Erkennung von Defekten. Sind die Fehlerklassen bekannt, lassen sie sich anhand von Defektbildern aus der Produktion antrainieren. Hingegen bei unbekannten Bildern und der Anforderung, jede Abweichung zu erkennen, werden die Prüfstücke mit einem Golden Master verglichen. In jedem dieser Fälle sind meist kleine Netze einzusetzen, die Fehlerklassen und deren Varianten detektieren. AlexNet, SqueezeNet oder MobileNet sind typische Vertreter hierfür. Diese sind als Basis für spezifische Anpassungen und Verbesserungen der Netzarchitektur für die individuelle Anwendung einsetzbar. Nach dem Training folgt die FPGA-Implementierung für die Inference, das heißt eine weitere Möglichkeit, Ressourcen zu optimieren und die Klassifizierungsqualität zu erhöhen. Im Verhältnis zwischen Erkennungsgenauigkeit, Implementierungsgröße und Rechengeschwindigkeit bzw. Bandbreite werden bei Machine Vision vorrangig kleine, schnelle Netze eingesetzt.