Porenfreies Löten

Reflow-Löten ohne Gaseinschlüsse für CMOS-Sensoren

Die neuen CMOS-Sensoren mit Global Shutter Technologie von Sony setzen aktuell neue Maßstäbe in der industriellen Bildverarbeitung. So attraktiv die Sensoren von ihren aufnahmetechnischen Eigenschaften auch sind, so sehr stellen sie aufgrund ihres LGA-Gehäuses (Land-Grid-Array) mit seinem geringen Abstand zur Leiterplattenoberfläche eine Herausforderung bei der Herstellung einer qualitativ hochwertigen Lötverbindung dar.

Weptech elektronik in Landau setzt bereits seit 2011 erfolgreich eine spezielle Fertigungstechnologie ein, mit der heute auch die Sony CMOS-Sensoren im kostengünstigen Konvektions-Verfahren voidarm, d.h. mit wenigen, nur sehr kleinen Gaseinschlüssen, auf Leiterplatten aufgelötet werden können. Dies stellt die Langlebigkeit der Lötverbindung sicher – selbst bei sehr häufigen und starken Temperaturschwankungen.

Konvektionslöten mit Problemen

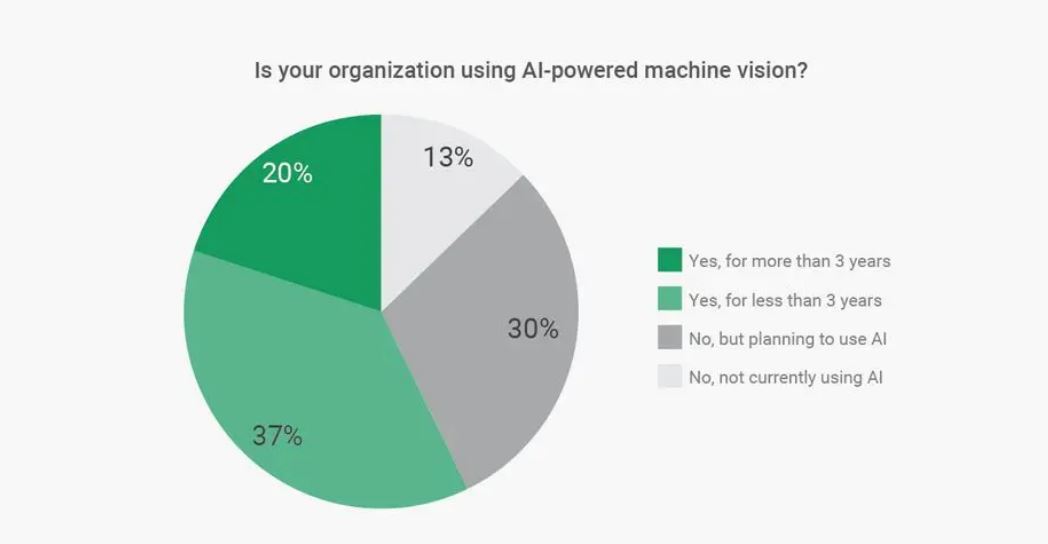

Beim herkömmlichen und kostengünstigsten Verfahren zur Kamerafertigung bestückt ein Automat die Leiterplatten mit sämtlichen elektronischen Bauteilen inklusive des Bild-Sensors und verfährt danach – ebenfalls automatisch – die Baugruppe in den direkt angeschlossenen Lötofen. Dieser verbindet die Bauteile im so genannten Reflow-Konvektionsverfahren elektrisch und mechanisch mit der Platine. Durch den hohen Automatisierungsgrad lassen sich auf diese Weise kleine wie große Stückzahlen schnell und kosteneffizient produzieren. Allerdings gelingt dies nur durch eine aufwendige und detaillierte Abstimmung von Leiterplattenoberfläche, Lotpaste und Lötprofil. In einem Standard-Lötprozess können bei den neuen CMOS-Sensoren mit LGA-Gehäuse die Kriterien der häufig geforderten Qualitätsnorm IPC-A610 hinsichtlich der Poren im Lot kaum prozessstabil erreicht werden (Bild 1a).

Alternative: Dampf-Löten mit Vakuum?

Bei großflächigen Lötstellen ist das Kondensationslöten (Dampfphasenlöten) mit Vakuum-Unterstützung ein probates Verfahren zur Herstellung von porenarmen Lötverbindungen. Das Verfahren wird häufig für Leistungskomponenten angewandt, bei denen neben der elektrischen Verbindung auch Kriterien wie die Wärmeleitung und Stromdichte eine Rolle spielen. Bei den genannten CMOS-Sensoren führen jedoch das recht hohe Gewicht und der geringe Abstand zur Leiterplattenoberfläche trotz optimierter Vakuum-Unterstützung zu suboptimalen Lötergebnissen. Zwar sinkt das Volumen der Poren auf eine akzeptable Größe, das Verschleppen von Lot durch den plötzlichen Gasaustritt aus der Lötstelle ist aber selbst bei feiner Vakuum-Dosierung nicht stabil zu verhindern (Bild 1b). Auch wirtschaftlich birgt dieses Verfahren Nachteile, da die Lötanlagen meistens nicht in vollautomatische Fertigungslinien integriert sind. Die oft manuelle Handhabung verursacht zusätzliche Kosten.